Hi all. Here I come again. With one week’s work, coreboot now can add romstage to the romfile, pass control to the romstage and find ramstage. I add a new way using a binary file to add stage to a rom file. Since I have not got an idea of how to store the hardware information, no hardware initialization is done now except the console. Following I will show you some snapshots:

This is a romfile without ramstage so it hangs at finding it:

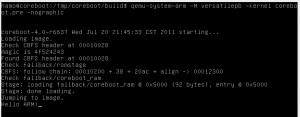

This is a romfile with a simple ramstage. The ramstage code only sends a string “Hello ARM!” to the console then hangs there. It is compressed using LZMA in the romfile and should be decompressed and copied to the RAM at address 0x5000. This romfile is for testing the decompress function and move-jump function.

Next week, I will work on the ramstage. It is one of the hardest parts since we will deal with the hardware information. I need to design it and implement it. I want my code to be tested and reviewed early for that it is not only about implementation but also design. One could change an implementation with a low cost but couldn’t change a design with a low cost.

Thanks to God and Thanks to all the coreboot developers. Working with you all is so happy and fantastic!

Author: Hamo

GSoC2011: midterm report

Hi all. Welcome to my midterm report for project “porting coreboot to ARM”.

Summary

The goal of this project is porting coreboot to ARM and taking advantage of coreboot’s strength in properly configuring PCI, SAS, SATA and SCSI devices; fast boot times; and payload support.

For ARM SOCs, the device configuring is much easier than that for X86. Most device controllers are connected through the on-chip bus. So the mainly work is focus on porting the basic layout and helping tools to ARM architecture, including CBFS, cbfstool and the codes helping loading next stage and payload into ram.

Changes to this project

At first, I want to work on Marvell ARM SOCs with PCIE support, but after checking into it, I found that mostly all the information and SDK of Marvell SOCs are covered under an NDA license. So I moved to VersatilePB from Armltd.

What works now

- CBFS record the architecture information in the master header

- cbfstool can detect the architecture of a rom file

- cbfstool can create an ARM rom file with bootblock

- bootblock for VersatilePB is ready for use

- romstage code for VersatilePB has been written

What doesn’t work (yet)

- cbfstool can not add-stage to the romfile due to a problem in prase_elf_to_stage

- romstage for VersatilePB has not been tested

- ramstage code for VersatilePB has not been written

What needs work

- design the information struct of hardware for payload on ARM

In this week, I will try to fix the problem of add-stage on ARM and test the romstage code.

Got any feature suggestions/ideas ?

GSoC2011(Week 5): the layout of coreboot rom and cbfstool for ARM

Hi all. How time flies. It has been 4 weeks since my last post. During this month, I have finished the design and implement of bootblock, Rom structure and cbfstool for ARM. Following I will show my changes to you all.

Continue reading GSoC2011(Week 5): the layout of coreboot rom and cbfstool for ARM

GSoC2011(Week 1): Analysis of U-boot ARM boot code

This is such a busy week. At the end of last week, I have just ordered my OpenRD-Ultimate box but sadly it will be delivered at the end of June. So if I just wait for that box, I will not be able to test my code. That’s terrible! After talking with my mentor, I decided first porting coreboot to RealView Versatile/PB926EJ-S board then to OpenRD-Ultimate. Since qemu can emulate PB926EJ-S, I can test my code on it quickly and freely. After this work, the basic layout, libs and headers for ARM are ready to use. So I can start to port coreboot to OpenRD-Ultimate then.

Continue reading GSoC2011(Week 1): Analysis of U-boot ARM boot code

GSoC2011 Project: Porting coreboot to ARM architecture

I am so excited that my idea on porting coreboot to ARM architecture has been accepted by GSoC project this year. First, let me introduce myself to you all. I am now a junior student at Hebei University of Technology, People’s Republic of China. My major is Computer Science and Technology. Although my courses are almost focus on high-level software development like database system and software engineering, I am a fan of low-level development. I taught myself IA32 and ARM architecture last year. And during this summer, we will porting coreboot to ARM and make it a new bootloader for ARM.

Those days, I am studying the building system of coreboot deeply, and I am trying to add cross-compile toolchain support to it. Developers has created such a great system and I want to make it greater. 🙂

Thanks for reading my project and any comment is welcome.