Hello!

During weeks 10, 11 and 12 I worked on:

- functions for gathering hardware specific data

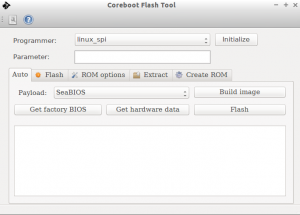

- automating process of building coreboot image

- GUI improvements

GATHERING HARDWARE SPECIFIC DATA

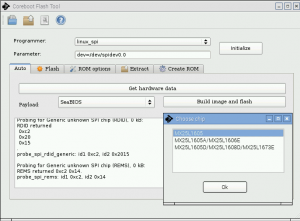

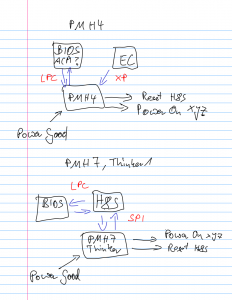

As I mentioned in my last post, if coreboot image should be built automatically then application needs to collect hardware specific data. During last weeks I added functions responsible for:

- dumping VGABIOS from memory: Some systems (like Lenovo T60 with ATI graphics) require adding VGABIOS dumped from memory to coreboot image, because factory BIOS patches it at runtime, so in certain cases using option rom extracted from factory BIOS may not work

- getting EDID data: to know what type of display panel is used in system

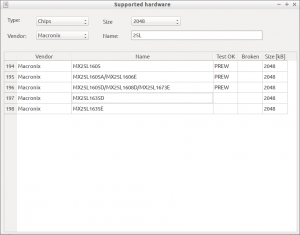

- getting motherboard model name: this is mandatory to recognize if we can install coreboot in system or if we have known working configuration

AUTOMATING PROCESS OF BUILDING COREBOOT IMAGE

It is now possible to build and flash coreboot image by clicking few application buttons without taking care which options are correct for system. Of course this is not possible for all hardware configurations, for now this is very limited, but with time database of known good configurations will grow and more users will be able to flash coreboot in such easy way.

Process of automated image building:

- Check if working configuration for system is known.

- Check if configuration requires additional option rom.

- If necessary, add option rom extracted from factory bios or extracted from running system memory.

- Build image.

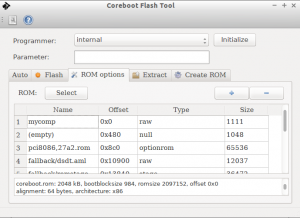

GUI IMPROVEMENTS

I decided to change a look of ‘ROM options’ tab. Previously just raw output of cbfs_tool with rom contents info was redirected to GUI log window. Now it is visible in a form of table, what in my opinion is more readable.

LAST WEEK AND FURTHER PLANS

GSoC “pencils down” date is coming up on Friday, so only few days are left. I want to use this time for:

- writing project documentation

- looking for bugs and fix them

- code cleanup

- adding new working configurations and testing them (I need your help with it)

- change debug messages to information popups

What after GSoC? I would like to still contribute, there is place for many improvements and possible extensions.