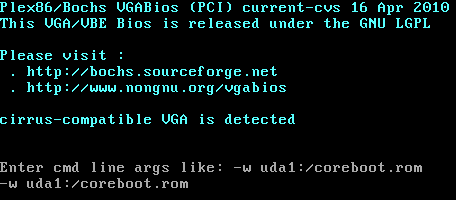

My project mostly involves to build an image with a small linux systemrunning a spice client, the system is attached with/as a LAB tocoreboot.

What was done

My buildrom tree received some updates and small changes to the building system. The bigest problem to solve was make it build coreboot with the new [k]build system. For that I changed build rom to incorporate the coreboot options so the user can configure every aspects of coreboot – all from buildrom menus. 🙂

For prototyping I used a chroot with a debian bootstrap(debootstrap), this surely doesn`t fit well to the project but I didn`t much attention for that, I thought I could leave it for second half – in the last days talking to my mentor I realized I should have paid more attention to the image things.

With a debootstrap I hacked I small script to package copy that root to my final image, what, once again, doesn`t fit our needs and requirements and here comes the tasks to be taken in the second half.

Second half

The project has been designed to be fully installed in/loaded from flash, It`s loaded with filo(but like discussed with my mentor any other bootload would fit prefectly).

Busybox will be our base system and a x-server. To acomplish that I have to take and finish the following tasks:

- design the building strategies which involves;

- building the busybox(well, this one is already done once we have a busybox package in buildrom system – I just need to base on that);

- select the needed x-server componentes(modules – Xlibs, Xprogs, Xvesa);

- select the alsa packages;

- include the spice client and its dependencies;

- define the kernel features;

- define how filo is about to load the final image;

- define the best compression algorithm;

- integrate the whole thing to buildrom;

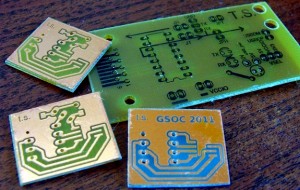

- alix board support;

The base building scripts will be packaged separetely and then integrated to buildrom like the other packages(i.e busybox, filo, grub and so on).

There`re just 6 weeks to the final evaluation and I`m leaving the alix board support to the last 2 weeks.

The build scripts and kernel prototyping will take the 2 first weeks, while the third one I`ll be working to put everything to be built by buildrom, the system can be tested as a proper system from an iso image till I get to integrate it to buildrom and package it as a coreboot payload.